Links

- Technical Discussion

- Complete Links

- Packium->Kirukkal

- Packium->Cool/Fun

- Packium->Storie s

- Packium->photo s

- Packium->hindib logs

- Packium->Techy< /a>

- Packium-> Tips

- Packium-> Samayal

- Count the number of bits set in an unsigned integer.

- E-Books for IT professionals

- Embedded stuffs .....

- how? y?

- Priority Inversion

- Technical discussion in yahoo chat - STB

- about ARM7TDMI

Previous Posts

Technical Discussion

Monday, November 06, 2006

Count the number of bits set in an unsigned integer.

/*

Program to count no. of bits in an unsigned integer

- C Language

*/

#include

#include

void main( void )

{

unsigned int a = 15;

int count = 0;

while( a )

{

++count;

a = a & ( a - 1 );

}

clrscr();

printf( "Count is %d\n", count );

getch();

}

Program to count no. of bits in an unsigned integer

- C Language

*/

#include

#include

void main( void )

{

unsigned int a = 15;

int count = 0;

while( a )

{

++count;

a = a & ( a - 1 );

}

clrscr();

printf( "Count is %d\n", count );

getch();

}

Friday, October 14, 2005

E-Books for IT professionals

Good Site for Software Engineers http://software-engineer.org/

No. Title/Author

1 10 minute guide to lotus notes mail 4.5

http://www.parsian.net/set1252/pages/books.htm

2 10 minute guide to Microsoft exchange 5.0

http://www.parsian.net/set1252/pages/books.htm

3 10 minute guide to outlook 97

http://www.parsian.net/set1252/pages/books.htm

4 10 minute guide to schedule+ for windows 95

http://www.parsian.net/set1252/pages/books.htm

5 ActiveX programming unleashed

http://www.parsian.net/set1252/pages/books.htm

6 ActiveX programming unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

7 Advanced perl programming

http://www.hk8.org/old_web/

8 Advanced PL/SQL programming with packages

http://www.hk8.org/old_web/

9 Adventure in Prolog/AMZI

www.oopweb.com

10 Algorithms CMSC251/Mount, David

www.oopweb.com

11 Alison Balter's Mastering Access 95 development, premier ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

12 Apache : The definitive guide, 3rd.ed.

http://www.hk8.org/old_web/

13 Beej's guide to network programming/Hall, Brain

www.oopweb.com

14 Beyond Linux from Scratch/BLFS Development Team

http://book.onairweb.net/computer/os/linux/Administration/Beyond_Linux_From_Scratch/

15 Borland C++ builder unleashed

http://www.parsian.net/set1252/pages/books.htm

16 Building an intranet with windows NT 4

http://www.parsian.net/set1252/pages/books.htm

17 Building an Intranet with Windows NT 4

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

18 Building expert systems in prolog/AMZI

www.oopweb.com

19 C programming language

http://book.onairweb.net/computer/pl/C/The_C_Programming_Language_by_K&R/

20 C Programming/Holmes, Steven

www.oopweb.com

21 C++ Annotations

www.oopweb.com

22 CGI developer's guide

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

23 CGI manual of style

http://www.parsian.net/set1252/pages/books.htm

24

CGI manual of style online

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

25 CGI programming

http://www.hk8.org/old_web/

26 CGI programming unleashed

http://www.parsian.net/set1252/pages/books.htm

27 CGI programming with Perl, 2nd.ed.

http://www.hk8.org/old_web/

28 Charlie Calvert's Borland C++ builder unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

29 Client/server computing, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

30 Client-server computing, 2nd.ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

31 Common LISP, the language/Steele, Guy

www.oopweb.com

32 Compilers and compiler generators : an introduction with C++/Terry, P.D.

www.oopweb.com

33 Complete idiot's guide to creating HTML webpage

http://www.parsian.net/set1252/pages/books.htm

34 Computer graphics CMSC 427/Mount, David

www.oopweb.com

35 Configuring and troubleshooting the windows NT/95 registry

http://www.parsian.net/set1252/pages/books.htm

36 Creating commercial websites

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

37 Creating web applets with Java

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

38 Crystal Reports.NET

http://www.crystalreportsbook.com/Chapters.asp

39 Curious about the internet

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

40 Curious about the internet?

http://www.parsian.net/set1252/pages/books.htm

41 Dan appleman's developing activeX components with Visual Basic 5

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

42 Dan appleman's developing activex components with Visual Basic 5.0

http://www.parsian.net/set1252/pages/books.htm

43 Data structures CMSC420/Mount, David

www.oopweb.com

44 Database developer's guide with visual basic 4, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

45 Database developer's guide with Visual Basic 4, 2nd.ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

46 Database developer's guide with Visual C++ 4, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

47 Database developer's guide with Visual C++ 4, 2nd.ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

48 Design and analysis of computer algorithms CMSC451/Mount, David

www.oopweb.com

49 Designing implementing Microsoft internet information server

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

50 Designing implementing Microsoft proxy server

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

51 Developing for netscape one

http://www.parsian.net/set1252/pages/books.htm

52 Developing intranet applications with java

http://www.parsian.net/set1252/pages/books.htm

53 Developing personal oracle 7 for windows 95 applications

http://www.parsian.net/set1252/pages/books.htm

54 Developing personal Oracle 7 for windows 95 applications

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

55 Developing professional java applets

http://www.parsian.net/set1252/pages/books.htm

56 Developing professional java applets

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

57 DNS and BIND

http://www.hk8.org/old_web/

58 Doing objects with VB.NET and C#

http://vbwire.com/nl?6814

59 EAI/BPM Evaluation Series: IBM WebSphere MQ Workflow v3.3.2 & EAI Suite by

> Middleware Technology Evaluation Series, Phong Tran & Jeffrey Gosper

http://www.cmis.csiro.au/mte/reports/BPM_IBMwebsphereMQ332.htm

60 Effective AWK programming

http://book.onairweb.net/computer/os/shell/Effective_AWK_Programming/

61 Enterprise javabeans, 2nd .ed.

http://www.hk8.org/old_web/

62 Exploring java

http://www.hk8.org/old_web/

63 GNOME/Sheets, John

www.oopweb.com

64 Graph theory/Prof. Even

www.oopweb.com

65 Hacking java

http://www.parsian.net/set1252/pages/books.htm

66 How intranets work

http://www.parsian.net/set1252/pages/books.htm

67 How intranets work

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

68 How to program visual basic 5.0

http://www.parsian.net/set1252/pages/books.htm

69 How to use HTML 3.2

http://www.parsian.net/set1252/pages/books.htm

70 Html : The definitive guide

http://www.hk8.org/old_web/

71 HTML 3.2 & CGI unleashed

http://www.parsian.net/set1252/pages/books.htm

72 HTML 3.2 and CGI professional reference edition unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

73 HTML by example

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

74 Internet firewall

http://www.hk8.org/old_web/

75 Intranets unleashed

http://www.parsian.net/set1252/pages/books.htm

76 Introduction to object-oriented programming using C++/Muller, Peter

www.oopweb.com

77 Introduction to programming using Java/Eck, David

www.oopweb.com

78 Introduction to socket programming

http://book.onairweb.net/computer/network/An_Introduction_to_Socket_Programming/

79 Java 1.1 unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

80 Java 1.1 unleashed, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

81 Java 1.1 unleashed, 3rd.ed.

http://www.parsian.net/set1252/pages/books.htm

82 Java 114 documentation

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

83 Java AWT reference

http://www.hk8.org/old_web/

84 Java by example

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

85 Java developer's guide

http://www.parsian.net/set1252/pages/books.htm

86 Java developer's guide

http://www.emu.edu.tr/english/facilitiesservices/computercenter/booksli

No. Title/Author

1 10 minute guide to lotus notes mail 4.5

http://www.parsian.net/set1252/pages/books.htm

2 10 minute guide to Microsoft exchange 5.0

http://www.parsian.net/set1252/pages/books.htm

3 10 minute guide to outlook 97

http://www.parsian.net/set1252/pages/books.htm

4 10 minute guide to schedule+ for windows 95

http://www.parsian.net/set1252/pages/books.htm

5 ActiveX programming unleashed

http://www.parsian.net/set1252/pages/books.htm

6 ActiveX programming unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

7 Advanced perl programming

http://www.hk8.org/old_web/

8 Advanced PL/SQL programming with packages

http://www.hk8.org/old_web/

9 Adventure in Prolog/AMZI

www.oopweb.com

10 Algorithms CMSC251/Mount, David

www.oopweb.com

11 Alison Balter's Mastering Access 95 development, premier ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

12 Apache : The definitive guide, 3rd.ed.

http://www.hk8.org/old_web/

13 Beej's guide to network programming/Hall, Brain

www.oopweb.com

14 Beyond Linux from Scratch/BLFS Development Team

http://book.onairweb.net/computer/os/linux/Administration/Beyond_Linux_From_Scratch/

15 Borland C++ builder unleashed

http://www.parsian.net/set1252/pages/books.htm

16 Building an intranet with windows NT 4

http://www.parsian.net/set1252/pages/books.htm

17 Building an Intranet with Windows NT 4

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

18 Building expert systems in prolog/AMZI

www.oopweb.com

19 C programming language

http://book.onairweb.net/computer/pl/C/The_C_Programming_Language_by_K&R/

20 C Programming/Holmes, Steven

www.oopweb.com

21 C++ Annotations

www.oopweb.com

22 CGI developer's guide

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

23 CGI manual of style

http://www.parsian.net/set1252/pages/books.htm

24

CGI manual of style online

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

25 CGI programming

http://www.hk8.org/old_web/

26 CGI programming unleashed

http://www.parsian.net/set1252/pages/books.htm

27 CGI programming with Perl, 2nd.ed.

http://www.hk8.org/old_web/

28 Charlie Calvert's Borland C++ builder unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

29 Client/server computing, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

30 Client-server computing, 2nd.ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

31 Common LISP, the language/Steele, Guy

www.oopweb.com

32 Compilers and compiler generators : an introduction with C++/Terry, P.D.

www.oopweb.com

33 Complete idiot's guide to creating HTML webpage

http://www.parsian.net/set1252/pages/books.htm

34 Computer graphics CMSC 427/Mount, David

www.oopweb.com

35 Configuring and troubleshooting the windows NT/95 registry

http://www.parsian.net/set1252/pages/books.htm

36 Creating commercial websites

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

37 Creating web applets with Java

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

38 Crystal Reports.NET

http://www.crystalreportsbook.com/Chapters.asp

39 Curious about the internet

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

40 Curious about the internet?

http://www.parsian.net/set1252/pages/books.htm

41 Dan appleman's developing activeX components with Visual Basic 5

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

42 Dan appleman's developing activex components with Visual Basic 5.0

http://www.parsian.net/set1252/pages/books.htm

43 Data structures CMSC420/Mount, David

www.oopweb.com

44 Database developer's guide with visual basic 4, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

45 Database developer's guide with Visual Basic 4, 2nd.ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

46 Database developer's guide with Visual C++ 4, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

47 Database developer's guide with Visual C++ 4, 2nd.ed.

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

48 Design and analysis of computer algorithms CMSC451/Mount, David

www.oopweb.com

49 Designing implementing Microsoft internet information server

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

50 Designing implementing Microsoft proxy server

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

51 Developing for netscape one

http://www.parsian.net/set1252/pages/books.htm

52 Developing intranet applications with java

http://www.parsian.net/set1252/pages/books.htm

53 Developing personal oracle 7 for windows 95 applications

http://www.parsian.net/set1252/pages/books.htm

54 Developing personal Oracle 7 for windows 95 applications

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

55 Developing professional java applets

http://www.parsian.net/set1252/pages/books.htm

56 Developing professional java applets

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

57 DNS and BIND

http://www.hk8.org/old_web/

58 Doing objects with VB.NET and C#

http://vbwire.com/nl?6814

59 EAI/BPM Evaluation Series: IBM WebSphere MQ Workflow v3.3.2 & EAI Suite by

> Middleware Technology Evaluation Series, Phong Tran & Jeffrey Gosper

http://www.cmis.csiro.au/mte/reports/BPM_IBMwebsphereMQ332.htm

60 Effective AWK programming

http://book.onairweb.net/computer/os/shell/Effective_AWK_Programming/

61 Enterprise javabeans, 2nd .ed.

http://www.hk8.org/old_web/

62 Exploring java

http://www.hk8.org/old_web/

63 GNOME/Sheets, John

www.oopweb.com

64 Graph theory/Prof. Even

www.oopweb.com

65 Hacking java

http://www.parsian.net/set1252/pages/books.htm

66 How intranets work

http://www.parsian.net/set1252/pages/books.htm

67 How intranets work

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

68 How to program visual basic 5.0

http://www.parsian.net/set1252/pages/books.htm

69 How to use HTML 3.2

http://www.parsian.net/set1252/pages/books.htm

70 Html : The definitive guide

http://www.hk8.org/old_web/

71 HTML 3.2 & CGI unleashed

http://www.parsian.net/set1252/pages/books.htm

72 HTML 3.2 and CGI professional reference edition unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

73 HTML by example

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

74 Internet firewall

http://www.hk8.org/old_web/

75 Intranets unleashed

http://www.parsian.net/set1252/pages/books.htm

76 Introduction to object-oriented programming using C++/Muller, Peter

www.oopweb.com

77 Introduction to programming using Java/Eck, David

www.oopweb.com

78 Introduction to socket programming

http://book.onairweb.net/computer/network/An_Introduction_to_Socket_Programming/

79 Java 1.1 unleashed

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

80 Java 1.1 unleashed, 2nd.ed.

http://www.parsian.net/set1252/pages/books.htm

81 Java 1.1 unleashed, 3rd.ed.

http://www.parsian.net/set1252/pages/books.htm

82 Java 114 documentation

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

83 Java AWT reference

http://www.hk8.org/old_web/

84 Java by example

http://www.emu.edu.tr/english/facilitiesservices/computercenter/bookslib/

85 Java developer's guide

http://www.parsian.net/set1252/pages/books.htm

86 Java developer's guide

http://www.emu.edu.tr/english/facilitiesservices/computercenter/booksli

Wednesday, July 13, 2005

Embedded stuffs .....

http://www.learn-c.com/data_lines.htm -> data bytes,words,nibbles,HEX

http://www.learn-c.com/boolean.htm -> Boolean logic

http://www.learn-c.com/adlines.htm -> Address lines & ports

http://www.learn-c.com/schemat.htm -> schematic

http://www.learn-c.com/hardware.htm -> the hardware

http://www.learn-c.com/alltoget.htm -> controlling hardware with software

http://www.learn-c.com/experiment1.htm -> basic switch detection

http://www.learn-c.com/experiment4.htm -> General purpose digital input output module

http://www.learn-c.com/experiment5.htm -> controlling motors

http://www.learn-c.com/experiment6.htm -> controlling motors II

http://www.learn-c.com/experiment7.htm -> hi switches

http://www.learn-c.com/experiment8.htm -> digital to analog convertion

http://www.learn-c.com/experiment9.htm -> Analog to digital convertion

http://www.learn-c.com/experiment9.htm -> analog reference control of motors

http://www.learn-c.com/experiment11.htm -> bi directional analog reference control

http://www.learn-c.com/boolean.htm -> Boolean logic

http://www.learn-c.com/adlines.htm -> Address lines & ports

http://www.learn-c.com/schemat.htm -> schematic

http://www.learn-c.com/hardware.htm -> the hardware

http://www.learn-c.com/alltoget.htm -> controlling hardware with software

http://www.learn-c.com/experiment1.htm -> basic switch detection

http://www.learn-c.com/experiment4.htm -> General purpose digital input output module

http://www.learn-c.com/experiment5.htm -> controlling motors

http://www.learn-c.com/experiment6.htm -> controlling motors II

http://www.learn-c.com/experiment7.htm -> hi switches

http://www.learn-c.com/experiment8.htm -> digital to analog convertion

http://www.learn-c.com/experiment9.htm -> Analog to digital convertion

http://www.learn-c.com/experiment9.htm -> analog reference control of motors

http://www.learn-c.com/experiment11.htm -> bi directional analog reference control

how? y?

if int i = 24 * 60 * 60 * 1000 * 1000 if we print it gives a value 500654080.

Actually it should give 86400 000 000

How? this is the question?

u are declaring the variable i as int. As u know, in java, int data type will occupy 4 bytes (32 bits). Therefore the range will be as below,

i.e. FROM 10000000000000000000000000000000 TO 01111111111111111111111111111111 (in binary)

i.e. FROM -2147483648 TO +2147483647 (in decimal)

i.e. FROM 0x80000000 TO 0x7FFFFFFF (in hex)

Ok now let me explain the problem.

the value given is 24 * 60 * 60 * 1000 * 1000.

As said it is equal to 86400 000 000.

and in binary it is 1010000011101110101110110000000000000.

obviously it needs 37 bits to store this value into system memory.

but we are assigning it into an int variable, or in other words u are storing the value into 32 bits... so the most signifigant 5 bits will be omitted (i.e. 10100 will be left over). Therefore the value stored wud be

11101110101110110000000000000 (in binary)

i.e. 500654080 (in decimal.) and hence the answer.

In general if the value requires more bits than the number of bits of the data type, then the most significant bits will be truncated (as many number of MSB bits will be truncated as required to make fit into the data type). This is how the behaviour will be with any language.

Tuesday, February 01, 2005

Priority Inversion

Priority Inversion

Any time two tasks share a resource, such as a memory buffer, in a system that employs a priority-based scheduler, one of them will usually have a higher priority. The higher-priority task expects to be run as soon as it is ready. However, if the lower-priority task is using their shared resource when the higher-priority task becomes ready to run, the higher-priority task must wait for the lower-priority task to finish with it. We say that the higher-priority task is pending on the resource. This situation is called priority inversion.

The state of a concurrent system where a high priority task is waiting for a low priority task which is waiting for a medium priority task. The system may become unstable and crash under these circumstances.

Avoiding the periority inversion through periority celing or periority inheritance.

Any time two tasks share a resource, such as a memory buffer, in a system that employs a priority-based scheduler, one of them will usually have a higher priority. The higher-priority task expects to be run as soon as it is ready. However, if the lower-priority task is using their shared resource when the higher-priority task becomes ready to run, the higher-priority task must wait for the lower-priority task to finish with it. We say that the higher-priority task is pending on the resource. This situation is called priority inversion.

The state of a concurrent system where a high priority task is waiting for a low priority task which is waiting for a medium priority task. The system may become unstable and crash under these circumstances.

Avoiding the periority inversion through periority celing or periority inheritance.

Sunday, January 30, 2005

Technical discussion in yahoo chat - STB

Date : 29 jan 2005

Time : 10.45Am to 1.40 PM

Members: Yuva,Giri,Prakash,Vijay,Manikandan,myself

Contributed by Yuva:

->Actually DVB is a wrapper to MPEG-2 standard

->MEG-2 defines PSI table, DVB defines SI tables

->According to MPEG-2 definition, these 4 tables PAT, PMT, NIT, CAT are important

->As for DVB, the following tables are important (remiaining are optional)

->Mandatory - NIT, SDT, EIT, TDt, Optional - other stream NIT, BAT, ...

->These are all about DVB and MPEG-2, and their relationship

->I would like to say about how these tables are formed

-> we will be having a raw data, which is said as elementary stream (eg audio, video, ttxt, ... )

->This lememntary stream, is first splitted into 64KB blocks, having header for each 64KB and then this partitioned data, is further splitted into packets of size 188 bytes

-> here is one point

-> DVB specifies, this packet formation in two ways - 1. Programm Stream, 2. Transport Stream

-> 1. Program Stream will have variable bit-rate elementary streams (i hope u all know what i mean variable bit-rate)

-> this Programm stream is used for DVD

-> 2. Transport Stream which will have constant bi-rate elementary streams, it is used in DVB

-> while encoding the analog signals (that is captured by camera, or by any speaker), this analog is converted into digital MPEG-2 data

-> the amount of bits required for encoding single frame (in case of video), the amount of bits required for single amplitued (in case of audio) is called bit-rate

-> that is, in video, we will be having several frames (here frame means, just visualize as a photo)

-> each frame will have different picture (tree in left in one picture, the same tree in another place)...

-> so, for each frame, we need different no. of bits (based on the redundancy data available in that frame)

-> so, for each frame, the no. bits vary, this gives variable-bit-rate

-> if we fix the bit-rate, fixed size, it gives constant bit-rate (in this case, there will be data loss)

-> in DVD, we can have variable-bit-rate, in which case we can use Programm stream format because the data is going to be in a fixed-medium, that is the disk, so at any time, the data is not going to change. This gives us the chance to have variable-bit-rate but for DVB (that is transmission) we cant have variable-bit-rate, because the carrier band-width is always fixed that we cant change, the broadcaster has to transmit all the programms within that band - this restriction forces to constant-bit-rate so DVB transmission uses Transport Stream format

->there is no much difference between Programm stream and Transport stream -we can convert from and to... (that i dont know, also i think not needed)

-> let me say about Transport stream only (if u want to know about Program stream, plz read ISO 13818-1)

-> So, in this Transport stream format, the elementary-stream bit-rate is always fixed

-> So, the multiplexer can easily mix all the data to form single transport stream

->This is general info about ES, TS

-> PES is nothing but the stream which is packetized to 188 bytes

-> ES -> [ 64KB partitioning ] -> PES -> TS

-> in the above, i said 64KB parititioning, which is done only for MPEG-2 defined tables

-> for DVB tables, there is no such thing

-> now we know that we are having several tables defined by both MPEG-2 and DVB

-> how do we distinguish and find the required tables is next

-> answer is given by PAT, which is the ROOT table givien details about all the tables present in given TS

-> DVB defines, the PAT table_id is 0x00 and PID ix 0x0000

-> PAT - Program Association Table

-> This PAT, will give information about how many programs transmitted in current TS

-> that is, unique Program Number ( unique to current stream ), its PMT

-> PMT - Program Map Table, which details about the ES (corresponding to the service_id mapped) available in current stream

-> PMT will give ES details, by listing PID value associated to particular ES

-> apart from these two tables, we have NIT and CAT

-> NIT - Network Information Table, gives information about Current TS

-> an example of PAT TABLE

Pg no PMT PID

0x1 0x324

0x2 0x111

0x0 0x15 (special case) this is not PMT PID instead it wud b NIT PID

-> that is pgm no and PMT PID

->the third case is a special case that is if the pgm no is xmitted as zero then the cor PID will tell u the NIT PID not the PMT PID

-> CAT - gives information about the encyption used

->Earlier i said generally, MPEG-2 Tables and DVB Tables, Transmission format is same ( trasmitted as packet, size - 188 Bytes )

->but the structure format is different

-> MPEG-2 ES are transmitted directly as ES -> 64KB -> PES -> Muxing -> Tranmission

->but DVB Tables are transmitted as ES -> Sections -> PES -> Muxing -> Transmission

-> MPEG-2 ES can be collected from PID obtained from PMT

-> DVB Tables also same, but the transmission data is sectioned (format is specified by DVB)

-> DVB Tables are sectioned and then converted to PES

-> but MPEG-2 Tableas are directly converted to PES

-> this is the differenence i said

-> This has to be noted because

->while requesting data from PTI, for DVB tables we request to give data as Sections

-> but for MPEG-2 Tables,we request using PID

-> For MPEG-2 format, plz study ISO 13818-2, 3 for video and audio respectively.

->the section format is some what same for all tables

section_name()

{

table_id

section_syntax_indicator

reserved_for_furutre_use

reserver

section_length

data_specific_to_the_current_defining_table

}

->In the above, if u take any table, the above listed details are same except,

'data_specific_to_the_current_defining_table'

-> which is specific to current defining table, if u check ETSI EN 300468, u can find this easily

-> the section_syntax_indicator, always '1' to all DVB standard tables except for private tables

->this 1 bit variable, indicate the structure format changes follwing section_length

-> RTOS : An OS defined specifically used in real-time system that respond to external events within a short and predictable time frame.

->1.PES also 188 byte and TS also 188 byte what is the difference between the two

->PES is constructed from ES.. PES has data only of that ES......TS is a mux of PES's

->In the ISO 1381-1 doc, plz check page no.68, there you can get details about table_id, section_synctax_indicator, ...

Contributed by Giri:

-> There ll b a inbuilt controller called DMA controller which ll do direct access to memory (SDRAM) without the knowledge of CPU in our ST MC

-> so our ST MC has a 32 bit address space

-> as u know the range wud b from 0x00000000 to 0xFFFFFFFF (32 bit) if it is unsigned address

->but ST is signed address space so it ll b from 0x80000000 to 0x7FFFFFFF

-> in that figure u can c the address started from 0x00000000 - 0xFFFFFFFF and they partitioned as 4 equal parts

-> the total mem size is 4 GB

-> each partion (Region) will have 1 GB

->As i told it is signed address so the start address wud b 0x80000000 that is region 0

-> look at it

-> got it reg 0 --- reg3?

->u jus add 0x40000000 = > 1GB with start address

-> u ll get next reg start address

-> now let me tell u abt each region

-> first region 0- in this region an ONCHIP SRAM ll b there (built in with the micro controller)

-> the size of the SRAM is 8 KB

-> v have 1 GB memory

-> but only 8 KB is accessible

-> other (1GB - 8KB) is reserved

-> under this 8 KB, 2 K is for instruction cache

-> but u ll have a provision to enable/disable the i cache

-> even if u r not enabe the icahce, u can not use that 2 KB for other purpose

-> that is reserver for i cache only

-> so u have remaining 6 KB

-> underthis 6 KB SRAM, 2 KB is for DATA cahce

-> u ll have a provision to enable/disable DCache

-> but it is important that..if u r not enable Data cache

->u can use that 2 KB for other purpose

-> CAN USE DCACHE MEM for other purpose

->so if u enable D cahe u ll have 4 KB and u disble it u ll have 6 KB

-> in that 6 KB u can place critical code ..if u want to run fast

-> as the sram is built in if u place code there the execution ll b much faster comparetively

-> but u can use it only for critical code

->as the mem size is too small

-> for example u have a function that has to b accessed every time and that take execution time much in that case u can place that code in SRAM

->live example

-> for font plotting

-> they ll b having an array char arry of size 720 bytes

-> this array has to b filled for each plotting

-> so they ll place that array in SRAM

-> it is not that such and such a code only b placed in SRAM

-> ok thats all abt SRAM i mean region 0

-> now Region 1

->hope u remember that i am talking abt 5518

-> Region 1 is called SMI

-> Shared memory interface

-> here there ll be an SDRAM

-> the maximum size possible is 8 MB

-> but it is not that it shd have 8 MB always

-> v can configure two 2 MB SDRAMS ( 4MB)

-> 2*4MB SDRAM (8mb)

-> 1*8MB(SDRAM)

-> but max size shd notexceed 8 MB (in 5518)

-> actually this memory wud b accessed by CPU and some other decoders (A/V decoder, DMA, OSD decoder etcc)

-> thats y v call it as SMI (Shared memory interface)

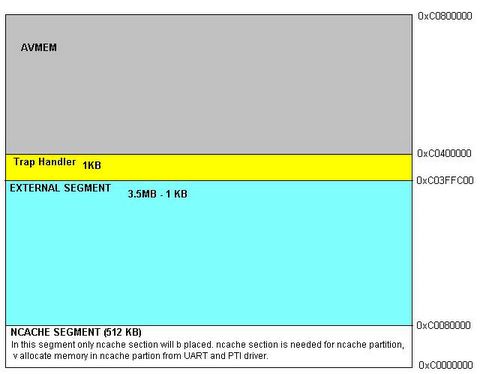

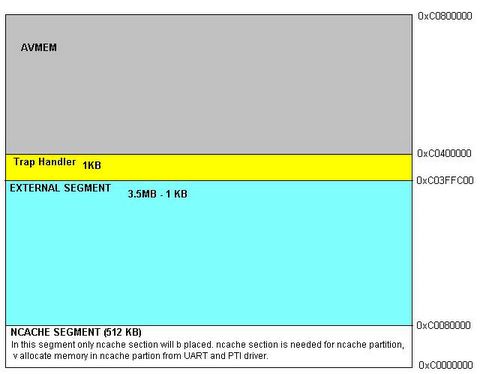

-> Earlier drawn SDRAM MAP is not completed

-> ok i ll xplain here

-> this is an example map

-> but v can also change it

-> the 8MB is devided as 4 segments (some lagical partitioning)

-> NCAcHE =>512 KB

-> EXTERNAL + TRAP = > 3.5 MB

->AVMEM=> 4 MB

->if a memory is cached and if the CPU wants to access to taht cache memory

-> then it ll not access the memory directly

-> instead it wud access it from the cache memory ( u remember 2 KB data cahe SRAM)

-> that is one copy of that memory ll also b in Cache like duplication

-> now u may have a doubt that have 8 MB sdram but only 2 K SRAM

-> actually whan the CPU accesses to memory

->it will first copy the 2KB of data from the accessed memory to that data cache and it ll do further r/w at cache alone

-> suppose in cache it needs access to the memory but that memory value is not in cache means the CPU write back the cache data to the original mem ( that is the other memory which is not cached ) and ll copy the new memory copy to cache

-> in 5518 v have 2 possiblities to CACHE SMI MEMORY

-> actually v can chache 1MB or 8 MB

->in one MB case u ll b having a 16 bit register

->and if u write all the 16 bits to 1

->it means u ve chched 1 MB

-> suppose if u set 5 bits

-> it meant that u cached 5 * 64 KB

-> athavathu u can cache block by block

-> each block of size 64 KB

-> as it is a 16 bit reg

-> max upto 16 * 64 KB = 1 MB

-> another category is 512 KB blocks

->so in this case u can chase the whole 8 MB

-> that is 16 * 512 KB = 8 MB

-> but v wont cache all the 512 blocks

-> b cos v need NCAHCE memory and also v wont cache AV mem

-> i told PTI needs NCACHE memory

-> becos the pti driver ll have direct access to the memory if u cahe taht pti memory

->the PTI ll always write data in MEMORY (direct access)

-> whereas the CPU readback the data from cache

-> so u ll end up with a problem

-> s the mem given to pti shd not b cached

-> abt EXTERNAL

-> this ll always b cached

-> but it is user wish (may/may not b cached)

->suppose if u run the code in lku mode the code, data, bss and const ll b placed here

-> actually in STM v he a good provition to place the code, data, const, bss wherever v wish

-> so user can create their own section within EXTERNAL to place them

->if the user doesnt create any section

-> the STM ll create a defualt section

-> in the name def_code, def_const, def_bss & def_data

-> but it is the user responsiblity to place them

-> for running a code as u know it needs stack and heap

->the stack and heap also given from this EXTERNAL segment

-> as our ST lite is multitasking os

-> many task can run concurrently so v have to give stack separately for each task

-> this is done as below

-> in configuration file v ll tell a stack size

-> this ll b taken for only root task that is main task

-> for all the user crated task (hope u remember task_create) v ll give the stack size as a paramer to the api call task_create

-> so the stlite ll take that much stack size for the user created task and always it ll take from the partion called (system_partition)

-> so it is the user responsiblity to create a partion with the name system_partiton and for this v need to create a section called system_section and it can b placed in EXTERNAL

-> what is the system partition min n max size?

-> actally there is no restriction in the size of system_partition .. actually after placing def_code, def_const, etc...

->it ll tell u the memory available in the EXTERNAL segment so by seeing that .. v can have that much mem for system_partition ( 1789952 byte - 1.7 MB )

Contributed by Prakash:

->if we say normally as "front end" means it includes both demod and tuner

-> demod means.. demodulator and tuner is as it as tuner

-> previously, both demod and tuner came by separately

-> now it combines both as NIM "Network Interface Model"

-> stv0299 is an example for satel. demod..stv0297 is for cable

-> there are so many companies such as samsung, LG, sharp are producing many tuners...

-> for satellite, the freq, symbol rate and polarization, fec is essential parameter. fec na.. forward error correction..

-> for terrestrail, the freq and constellation, FFT mode (2k or 8k)...

-> in this tuner we use bandwidth for searching the next freq.

-> purely depends on the datasheet for the particular chips..

-> so can give only general ideas only..

-> FFT ? fast fourier transform aah

-> in tuner, we have to set the freq.

-> in demod only... we need to set the all necessary parameters..

-> but each type of demod has different register (find it in datasheet).

-> basically we need to set the data in particular reg. as per the necessary parameter details.

-> in satellite, after set the freq. pol and s/r we need to check the corr. register

-> while reading the byte lock and sync lock and fec lock.

-> but in tuner, we need to set only freq. details.

-> some demod has the provision to acquire the noise signal ratio and Bit error rate...

-> we can decide the lock status according to get teh value of that corr. reg.

-> in samsung, lg, we can do to zigzag the freq. in both + or - value of the given freq. but fujitsu tuner, if we wait some time, after read the lock reg. we can decide that lock status..

-> if we mean, locked.. we can read the offset of freq. which actually locked..

-> ok.. about pvr small glance

-> if the user want to record some program in hard disk,

-> he can select the particular program and can store it in hdd.

-> there r so many categories in pvr box. twin tuner and single tuner and also..

-> nowadays, the some ST chips supports 2 or 3 PTI's to store and watch simultaneously.

-> if twin tuner supports that box, we can store the program in another satellite or carrier.

-> if single tuner means, can store the service which is from same tp....tp na carrier

-> so onchip memory process the data is same as..

-> do in normal.. we can store it into Hard Disk Drive using ATAPI (AT Attachement Packet Interface) command. in 5510 we r using 7 version..

-> in atapi command also.. it has the version like standard..

->tell abotu that interface

-> to interface from onchip to harddisk..

-> it has 2 mode.. pio mode or dma mode..

-> previously st chip supports only pio mode..

-> nowadays.. it includes dma and ultra dma..

-> it is configurable..

-> we can store the same as Transport Stream format as 204 bytes

-> as yuva said earlier..

-> another method is, parse the data and store teh neccessary data (elementary stream such as audio, video and PCR)

-> in TS method, there is no software burden... since we can inject the data, as same as from the air.

-> but in PES method.. there is parsing and storing the necessary data nad presentation time stamp (PTS) and decoding Time Stamp (DTS)..

-> need to calculate by software adn handle according while playback..

-> trickmode.. means.. fast forward, slow forward, backward..

-> it is also features in pvr application..

-> if we want to display the event information we have to store that data also...

General descussion:

-> wht is laterst CAS/CIS chip?

->the latest Chips r cis, stv0700...

-> what is the latest micro controller in market

-> i think ST5100, i am not sure

-> actualy for the past 3 yrs STi5518 is the most used ST CHIP others are STi5514, Sti5516 and Sti5517..now all r cocentrating with 5517

-> wat is difference in these chips

-> mainly these versions are for fast PVR support

-> ST5514, has dual PTI support, such that we can tune two different streams (even different delivary system) and has more support for PVR

-> 5516 has single PTI, but enhanved support for PVR (i dont know exatly the feature)

-> 5517 is extension for 5516, but some more support, like OSD (have 16-bit True color, ... )

-> moreover memory size wud b more

-> in 5517 ICAHCE is 8K

->dcache is 8K

-> SMI SDRAM size is 16 MB

-> 5516 and 5517 difference - Suitable for use in cable, terrestrial and satellite TV applications, the STi5517 builds on the success of the popular STi5516 by adding higher specification graphics (RGB16) and enhanced security features, enabling customers to manufacture cheaper and more secure STBs. In addition, the ST20 CPU speed has been increased to 180MHz, enabling a richer user experience through faster response times and the ability to support a wider range of

applications. Audio options include MP3 decoding, Dolby Digital and Pro Logic decoding and support for SRS TruSurroundÔ virtual surround sound. The STi5517 also includes a multi-channel DMA engine, which, in combination with the enhanced RGB16 graphics, makes the device particularly suitable for graphically rich applications such

DVB-MHP, browser based middlewares and low cost IPTV.

-> http://www.st.com/stonline/press/news/year2004/p1494p.htm

->A network is a single entity (e.g. a company) that broadcasts one or more transport streams

->A transport stream is an MPEG-2 stream containing several services

->Each service is a TV channel, and consists of a series of events one after the other

->Each event is a single TV show, and consists of a number of elementary streams

->Each elementary stream is a packetized MPEG-2 stream containing MPEG-2 encoded audio, video or binary data.

->Several services (possibly from several different transport streams) can be grouped together logically in a bouquet.

Every service can be uniquely identified by three values. These values are the original network ID (the ID of the network that originally broadcast the service), the transport stream ID (to identify a particular transport stream from that network) and a service ID to identify a service within that transport stream.

The SI tables that are commonly found in a DVB transport stream are:

Program Association table (PAT) - defined by the MPEG standard

Program Map Table (PMT) - defined by the MPEG standard

Network Information Table (NIT)

Service Description Table (SDT)

Event Information Table (EIT)

Conditional Access Table (CAT)

Bouquet Association Table (BAT)

Time and Date Table (TDT)

Time Offset Table (TOT)

The Program Association Table is the fundamental table for service information. It is the only table that is broadcast on a fixed PID, and it describes which PID contains the Program Map Table for each service (see below) as well as the Network Information Table for the transport stream.

The Network Information Table describes how transport streams are organized on the current network, and also describes some of the physical properties of the network itself. The NIT also contains the name of the network, and the network ID. This is a value that uniquely identifies the network that is currently broadcasting the transport stream, and may be different from the original network ID that we discussed earlier, if the transport stream is being rebroadcast.

The Conditional Access Table describes the CA systems that are in use in the transport stream, and provides information about how do decode them.

The Program Map Table is the table that actually describes how a service is put together. This table describes all the streams in a service, and tells the receiver which stream contains the MPEG Program Clock Reference for the service. The PMT is not broadcast on a fixed PID, and a transport stream will contain one PMT for each service it contains.

Together, the PAT, PMT, CAT and NIT are known as Program Specific Information (PSI) and are defined by MPEG, although MPEG specifies that the NIT is only optional, while the others are all mandatory. DVB strengthens this and makes the NIT mandatory as well.

The Service Description Table gives more user-oriented information about services in a transport stream. Unlike the PMTs, there is only one SDT in a transport stream, and that contains the information for every service. The SDT typically contains information such as the name of the service, the service ID, the status of the service (e.g. running/not running/starting in a few seconds) and whether the service is scrambled or not.

The Event Information Table provides schedule information about events on a service. This includes the event name, start time duration and the status of the event. It is mandatory for the transport stream to contain the EIT describing the present and following events (known as the EIT present-following), while information about other events is optional.

The Bouquet Association Table lists and describes the services in a bouquet. This does not provide very detailed information, since this can be gained from other SI tables. Instead, it just provides a list of the services contained in a bouquet.

The Time and Date Table and the Time Offset Table provide a time reference for the stream. The TDT contains the current UTC (Universal/GMT) time, while the TOT contains both this and the offset from UTC for local time. This can be used to calculate schedule information accurately, if needed.

Some of these tables may contain information about other transport streams, as well as information about the current transport streams. The NIT, SDT and EIT must contain information about the current transport stream (and these tables are known as the NIT-actual, SDT-actual and EIT-actual respectively), but the transport stream may also contain versions of these tables that refer to other transport streams. These are known as the NIT-other, SDT-other and EIT-other.

Time : 10.45Am to 1.40 PM

Members: Yuva,Giri,Prakash,Vijay,Manikandan,myself

Contributed by Yuva:

->Actually DVB is a wrapper to MPEG-2 standard

->MEG-2 defines PSI table, DVB defines SI tables

->According to MPEG-2 definition, these 4 tables PAT, PMT, NIT, CAT are important

->As for DVB, the following tables are important (remiaining are optional)

->Mandatory - NIT, SDT, EIT, TDt, Optional - other stream NIT, BAT, ...

->These are all about DVB and MPEG-2, and their relationship

->I would like to say about how these tables are formed

-> we will be having a raw data, which is said as elementary stream (eg audio, video, ttxt, ... )

->This lememntary stream, is first splitted into 64KB blocks, having header for each 64KB and then this partitioned data, is further splitted into packets of size 188 bytes

-> here is one point

-> DVB specifies, this packet formation in two ways - 1. Programm Stream, 2. Transport Stream

-> 1. Program Stream will have variable bit-rate elementary streams (i hope u all know what i mean variable bit-rate)

-> this Programm stream is used for DVD

-> 2. Transport Stream which will have constant bi-rate elementary streams, it is used in DVB

-> while encoding the analog signals (that is captured by camera, or by any speaker), this analog is converted into digital MPEG-2 data

-> the amount of bits required for encoding single frame (in case of video), the amount of bits required for single amplitued (in case of audio) is called bit-rate

-> that is, in video, we will be having several frames (here frame means, just visualize as a photo)

-> each frame will have different picture (tree in left in one picture, the same tree in another place)...

-> so, for each frame, we need different no. of bits (based on the redundancy data available in that frame)

-> so, for each frame, the no. bits vary, this gives variable-bit-rate

-> if we fix the bit-rate, fixed size, it gives constant bit-rate (in this case, there will be data loss)

-> in DVD, we can have variable-bit-rate, in which case we can use Programm stream format because the data is going to be in a fixed-medium, that is the disk, so at any time, the data is not going to change. This gives us the chance to have variable-bit-rate but for DVB (that is transmission) we cant have variable-bit-rate, because the carrier band-width is always fixed that we cant change, the broadcaster has to transmit all the programms within that band - this restriction forces to constant-bit-rate so DVB transmission uses Transport Stream format

->there is no much difference between Programm stream and Transport stream -we can convert from and to... (that i dont know, also i think not needed)

-> let me say about Transport stream only (if u want to know about Program stream, plz read ISO 13818-1)

-> So, in this Transport stream format, the elementary-stream bit-rate is always fixed

-> So, the multiplexer can easily mix all the data to form single transport stream

->This is general info about ES, TS

-> PES is nothing but the stream which is packetized to 188 bytes

-> ES -> [ 64KB partitioning ] -> PES -> TS

-> in the above, i said 64KB parititioning, which is done only for MPEG-2 defined tables

-> for DVB tables, there is no such thing

-> now we know that we are having several tables defined by both MPEG-2 and DVB

-> how do we distinguish and find the required tables is next

-> answer is given by PAT, which is the ROOT table givien details about all the tables present in given TS

-> DVB defines, the PAT table_id is 0x00 and PID ix 0x0000

-> PAT - Program Association Table

-> This PAT, will give information about how many programs transmitted in current TS

-> that is, unique Program Number ( unique to current stream ), its PMT

-> PMT - Program Map Table, which details about the ES (corresponding to the service_id mapped) available in current stream

-> PMT will give ES details, by listing PID value associated to particular ES

-> apart from these two tables, we have NIT and CAT

-> NIT - Network Information Table, gives information about Current TS

-> an example of PAT TABLE

Pg no PMT PID

0x1 0x324

0x2 0x111

0x0 0x15 (special case) this is not PMT PID instead it wud b NIT PID

-> that is pgm no and PMT PID

->the third case is a special case that is if the pgm no is xmitted as zero then the cor PID will tell u the NIT PID not the PMT PID

-> CAT - gives information about the encyption used

->Earlier i said generally, MPEG-2 Tables and DVB Tables, Transmission format is same ( trasmitted as packet, size - 188 Bytes )

->but the structure format is different

-> MPEG-2 ES are transmitted directly as ES -> 64KB -> PES -> Muxing -> Tranmission

->but DVB Tables are transmitted as ES -> Sections -> PES -> Muxing -> Transmission

-> MPEG-2 ES can be collected from PID obtained from PMT

-> DVB Tables also same, but the transmission data is sectioned (format is specified by DVB)

-> DVB Tables are sectioned and then converted to PES

-> but MPEG-2 Tableas are directly converted to PES

-> this is the differenence i said

-> This has to be noted because

->while requesting data from PTI, for DVB tables we request to give data as Sections

-> but for MPEG-2 Tables,we request using PID

-> For MPEG-2 format, plz study ISO 13818-2, 3 for video and audio respectively.

->the section format is some what same for all tables

section_name()

{

table_id

section_syntax_indicator

reserved_for_furutre_use

reserver

section_length

data_specific_to_the_current_defining_table

}

->In the above, if u take any table, the above listed details are same except,

'data_specific_to_the_current_defining_table'

-> which is specific to current defining table, if u check ETSI EN 300468, u can find this easily

-> the section_syntax_indicator, always '1' to all DVB standard tables except for private tables

->this 1 bit variable, indicate the structure format changes follwing section_length

-> RTOS : An OS defined specifically used in real-time system that respond to external events within a short and predictable time frame.

->1.PES also 188 byte and TS also 188 byte what is the difference between the two

->PES is constructed from ES.. PES has data only of that ES......TS is a mux of PES's

->In the ISO 1381-1 doc, plz check page no.68, there you can get details about table_id, section_synctax_indicator, ...

Contributed by Giri:

-> There ll b a inbuilt controller called DMA controller which ll do direct access to memory (SDRAM) without the knowledge of CPU in our ST MC

-> so our ST MC has a 32 bit address space

-> as u know the range wud b from 0x00000000 to 0xFFFFFFFF (32 bit) if it is unsigned address

->but ST is signed address space so it ll b from 0x80000000 to 0x7FFFFFFF

-> in that figure u can c the address started from 0x00000000 - 0xFFFFFFFF and they partitioned as 4 equal parts

-> the total mem size is 4 GB

-> each partion (Region) will have 1 GB

->As i told it is signed address so the start address wud b 0x80000000 that is region 0

-> look at it

-> got it reg 0 --- reg3?

->u jus add 0x40000000 = > 1GB with start address

-> u ll get next reg start address

-> now let me tell u abt each region

-> first region 0- in this region an ONCHIP SRAM ll b there (built in with the micro controller)

-> the size of the SRAM is 8 KB

-> v have 1 GB memory

-> but only 8 KB is accessible

-> other (1GB - 8KB) is reserved

-> under this 8 KB, 2 K is for instruction cache

-> but u ll have a provision to enable/disable the i cache

-> even if u r not enabe the icahce, u can not use that 2 KB for other purpose

-> that is reserver for i cache only

-> so u have remaining 6 KB

-> underthis 6 KB SRAM, 2 KB is for DATA cahce

-> u ll have a provision to enable/disable DCache

-> but it is important that..if u r not enable Data cache

->u can use that 2 KB for other purpose

-> CAN USE DCACHE MEM for other purpose

->so if u enable D cahe u ll have 4 KB and u disble it u ll have 6 KB

-> in that 6 KB u can place critical code ..if u want to run fast

-> as the sram is built in if u place code there the execution ll b much faster comparetively

-> but u can use it only for critical code

->as the mem size is too small

-> for example u have a function that has to b accessed every time and that take execution time much in that case u can place that code in SRAM

->live example

-> for font plotting

-> they ll b having an array char arry of size 720 bytes

-> this array has to b filled for each plotting

-> so they ll place that array in SRAM

-> it is not that such and such a code only b placed in SRAM

-> ok thats all abt SRAM i mean region 0

-> now Region 1

->hope u remember that i am talking abt 5518

-> Region 1 is called SMI

-> Shared memory interface

-> here there ll be an SDRAM

-> the maximum size possible is 8 MB

-> but it is not that it shd have 8 MB always

-> v can configure two 2 MB SDRAMS ( 4MB)

-> 2*4MB SDRAM (8mb)

-> 1*8MB(SDRAM)

-> but max size shd notexceed 8 MB (in 5518)

-> actually this memory wud b accessed by CPU and some other decoders (A/V decoder, DMA, OSD decoder etcc)

-> thats y v call it as SMI (Shared memory interface)

-> Earlier drawn SDRAM MAP is not completed

-> ok i ll xplain here

-> this is an example map

-> but v can also change it

-> the 8MB is devided as 4 segments (some lagical partitioning)

-> NCAcHE =>512 KB

-> EXTERNAL + TRAP = > 3.5 MB

->AVMEM=> 4 MB

->if a memory is cached and if the CPU wants to access to taht cache memory

-> then it ll not access the memory directly

-> instead it wud access it from the cache memory ( u remember 2 KB data cahe SRAM)

-> that is one copy of that memory ll also b in Cache like duplication

-> now u may have a doubt that have 8 MB sdram but only 2 K SRAM

-> actually whan the CPU accesses to memory

->it will first copy the 2KB of data from the accessed memory to that data cache and it ll do further r/w at cache alone

-> suppose in cache it needs access to the memory but that memory value is not in cache means the CPU write back the cache data to the original mem ( that is the other memory which is not cached ) and ll copy the new memory copy to cache

-> in 5518 v have 2 possiblities to CACHE SMI MEMORY

-> actually v can chache 1MB or 8 MB

->in one MB case u ll b having a 16 bit register

->and if u write all the 16 bits to 1

->it means u ve chched 1 MB

-> suppose if u set 5 bits

-> it meant that u cached 5 * 64 KB

-> athavathu u can cache block by block

-> each block of size 64 KB

-> as it is a 16 bit reg

-> max upto 16 * 64 KB = 1 MB

-> another category is 512 KB blocks

->so in this case u can chase the whole 8 MB

-> that is 16 * 512 KB = 8 MB

-> but v wont cache all the 512 blocks

-> b cos v need NCAHCE memory and also v wont cache AV mem

-> i told PTI needs NCACHE memory

-> becos the pti driver ll have direct access to the memory if u cahe taht pti memory

->the PTI ll always write data in MEMORY (direct access)

-> whereas the CPU readback the data from cache

-> so u ll end up with a problem

-> s the mem given to pti shd not b cached

-> abt EXTERNAL

-> this ll always b cached

-> but it is user wish (may/may not b cached)

->suppose if u run the code in lku mode the code, data, bss and const ll b placed here

-> actually in STM v he a good provition to place the code, data, const, bss wherever v wish

-> so user can create their own section within EXTERNAL to place them

->if the user doesnt create any section

-> the STM ll create a defualt section

-> in the name def_code, def_const, def_bss & def_data

-> but it is the user responsiblity to place them

-> for running a code as u know it needs stack and heap

->the stack and heap also given from this EXTERNAL segment

-> as our ST lite is multitasking os

-> many task can run concurrently so v have to give stack separately for each task

-> this is done as below

-> in configuration file v ll tell a stack size

-> this ll b taken for only root task that is main task

-> for all the user crated task (hope u remember task_create) v ll give the stack size as a paramer to the api call task_create

-> so the stlite ll take that much stack size for the user created task and always it ll take from the partion called (system_partition)

-> so it is the user responsiblity to create a partion with the name system_partiton and for this v need to create a section called system_section and it can b placed in EXTERNAL

-> what is the system partition min n max size?

-> actally there is no restriction in the size of system_partition .. actually after placing def_code, def_const, etc...

->it ll tell u the memory available in the EXTERNAL segment so by seeing that .. v can have that much mem for system_partition ( 1789952 byte - 1.7 MB )

Contributed by Prakash:

->if we say normally as "front end" means it includes both demod and tuner

-> demod means.. demodulator and tuner is as it as tuner

-> previously, both demod and tuner came by separately

-> now it combines both as NIM "Network Interface Model"

-> stv0299 is an example for satel. demod..stv0297 is for cable

-> there are so many companies such as samsung, LG, sharp are producing many tuners...

-> for satellite, the freq, symbol rate and polarization, fec is essential parameter. fec na.. forward error correction..

-> for terrestrail, the freq and constellation, FFT mode (2k or 8k)...

-> in this tuner we use bandwidth for searching the next freq.

-> purely depends on the datasheet for the particular chips..

-> so can give only general ideas only..

-> FFT ? fast fourier transform aah

-> in tuner, we have to set the freq.

-> in demod only... we need to set the all necessary parameters..

-> but each type of demod has different register (find it in datasheet).

-> basically we need to set the data in particular reg. as per the necessary parameter details.

-> in satellite, after set the freq. pol and s/r we need to check the corr. register

-> while reading the byte lock and sync lock and fec lock.

-> but in tuner, we need to set only freq. details.

-> some demod has the provision to acquire the noise signal ratio and Bit error rate...

-> we can decide the lock status according to get teh value of that corr. reg.

-> in samsung, lg, we can do to zigzag the freq. in both + or - value of the given freq. but fujitsu tuner, if we wait some time, after read the lock reg. we can decide that lock status..

-> if we mean, locked.. we can read the offset of freq. which actually locked..

-> ok.. about pvr small glance

-> if the user want to record some program in hard disk,

-> he can select the particular program and can store it in hdd.

-> there r so many categories in pvr box. twin tuner and single tuner and also..

-> nowadays, the some ST chips supports 2 or 3 PTI's to store and watch simultaneously.

-> if twin tuner supports that box, we can store the program in another satellite or carrier.

-> if single tuner means, can store the service which is from same tp....tp na carrier

-> so onchip memory process the data is same as..

-> do in normal.. we can store it into Hard Disk Drive using ATAPI (AT Attachement Packet Interface) command. in 5510 we r using 7 version..

-> in atapi command also.. it has the version like standard..

->tell abotu that interface

-> to interface from onchip to harddisk..

-> it has 2 mode.. pio mode or dma mode..

-> previously st chip supports only pio mode..

-> nowadays.. it includes dma and ultra dma..

-> it is configurable..

-> we can store the same as Transport Stream format as 204 bytes

-> as yuva said earlier..

-> another method is, parse the data and store teh neccessary data (elementary stream such as audio, video and PCR)

-> in TS method, there is no software burden... since we can inject the data, as same as from the air.

-> but in PES method.. there is parsing and storing the necessary data nad presentation time stamp (PTS) and decoding Time Stamp (DTS)..

-> need to calculate by software adn handle according while playback..

-> trickmode.. means.. fast forward, slow forward, backward..

-> it is also features in pvr application..

-> if we want to display the event information we have to store that data also...

General descussion:

-> wht is laterst CAS/CIS chip?

->the latest Chips r cis, stv0700...

-> what is the latest micro controller in market

-> i think ST5100, i am not sure

-> actualy for the past 3 yrs STi5518 is the most used ST CHIP others are STi5514, Sti5516 and Sti5517..now all r cocentrating with 5517

-> wat is difference in these chips

-> mainly these versions are for fast PVR support

-> ST5514, has dual PTI support, such that we can tune two different streams (even different delivary system) and has more support for PVR

-> 5516 has single PTI, but enhanved support for PVR (i dont know exatly the feature)

-> 5517 is extension for 5516, but some more support, like OSD (have 16-bit True color, ... )

-> moreover memory size wud b more

-> in 5517 ICAHCE is 8K

->dcache is 8K

-> SMI SDRAM size is 16 MB

-> 5516 and 5517 difference - Suitable for use in cable, terrestrial and satellite TV applications, the STi5517 builds on the success of the popular STi5516 by adding higher specification graphics (RGB16) and enhanced security features, enabling customers to manufacture cheaper and more secure STBs. In addition, the ST20 CPU speed has been increased to 180MHz, enabling a richer user experience through faster response times and the ability to support a wider range of

applications. Audio options include MP3 decoding, Dolby Digital and Pro Logic decoding and support for SRS TruSurroundÔ virtual surround sound. The STi5517 also includes a multi-channel DMA engine, which, in combination with the enhanced RGB16 graphics, makes the device particularly suitable for graphically rich applications such

DVB-MHP, browser based middlewares and low cost IPTV.

-> http://www.st.com/stonline/press/news/year2004/p1494p.htm

->A network is a single entity (e.g. a company) that broadcasts one or more transport streams

->A transport stream is an MPEG-2 stream containing several services

->Each service is a TV channel, and consists of a series of events one after the other

->Each event is a single TV show, and consists of a number of elementary streams

->Each elementary stream is a packetized MPEG-2 stream containing MPEG-2 encoded audio, video or binary data.

->Several services (possibly from several different transport streams) can be grouped together logically in a bouquet.

Every service can be uniquely identified by three values. These values are the original network ID (the ID of the network that originally broadcast the service), the transport stream ID (to identify a particular transport stream from that network) and a service ID to identify a service within that transport stream.

The SI tables that are commonly found in a DVB transport stream are:

Program Association table (PAT) - defined by the MPEG standard

Program Map Table (PMT) - defined by the MPEG standard

Network Information Table (NIT)

Service Description Table (SDT)

Event Information Table (EIT)

Conditional Access Table (CAT)

Bouquet Association Table (BAT)

Time and Date Table (TDT)

Time Offset Table (TOT)

The Program Association Table is the fundamental table for service information. It is the only table that is broadcast on a fixed PID, and it describes which PID contains the Program Map Table for each service (see below) as well as the Network Information Table for the transport stream.

The Network Information Table describes how transport streams are organized on the current network, and also describes some of the physical properties of the network itself. The NIT also contains the name of the network, and the network ID. This is a value that uniquely identifies the network that is currently broadcasting the transport stream, and may be different from the original network ID that we discussed earlier, if the transport stream is being rebroadcast.

The Conditional Access Table describes the CA systems that are in use in the transport stream, and provides information about how do decode them.

The Program Map Table is the table that actually describes how a service is put together. This table describes all the streams in a service, and tells the receiver which stream contains the MPEG Program Clock Reference for the service. The PMT is not broadcast on a fixed PID, and a transport stream will contain one PMT for each service it contains.

Together, the PAT, PMT, CAT and NIT are known as Program Specific Information (PSI) and are defined by MPEG, although MPEG specifies that the NIT is only optional, while the others are all mandatory. DVB strengthens this and makes the NIT mandatory as well.

The Service Description Table gives more user-oriented information about services in a transport stream. Unlike the PMTs, there is only one SDT in a transport stream, and that contains the information for every service. The SDT typically contains information such as the name of the service, the service ID, the status of the service (e.g. running/not running/starting in a few seconds) and whether the service is scrambled or not.

The Event Information Table provides schedule information about events on a service. This includes the event name, start time duration and the status of the event. It is mandatory for the transport stream to contain the EIT describing the present and following events (known as the EIT present-following), while information about other events is optional.

The Bouquet Association Table lists and describes the services in a bouquet. This does not provide very detailed information, since this can be gained from other SI tables. Instead, it just provides a list of the services contained in a bouquet.

The Time and Date Table and the Time Offset Table provide a time reference for the stream. The TDT contains the current UTC (Universal/GMT) time, while the TOT contains both this and the offset from UTC for local time. This can be used to calculate schedule information accurately, if needed.

Some of these tables may contain information about other transport streams, as well as information about the current transport streams. The NIT, SDT and EIT must contain information about the current transport stream (and these tables are known as the NIT-actual, SDT-actual and EIT-actual respectively), but the transport stream may also contain versions of these tables that refer to other transport streams. These are known as the NIT-other, SDT-other and EIT-other.

about ARM7TDMI

ARM7TDMI

---------------

->The ARM7TDMI is memeber of the advanced RISC MAchines ( ARM) family of general purpose 32 bit microprocessor.

->offers hifh performance for very low power consumption and price.

->It architecture is based on reduced instruciton set computer( RISC)

what is difference between RISC and CISC?

RISC->Reduced instrution set computer

CISC->Complex instrution set computer

Complex instructions came about in order to maximize the performance of early computers. At that time, computers executed instructions sequentially. The first instruction had to complete the execution cycle before the next instruction could begin. Designers combined sequences of instructions into single instructions. This reduced the amount of time spent retrieving instructions from memory , although these instructions did require multiple clocks cycles to execute.

RISC architecture makes use of a small set of simplified instructions in attempt to improve performance . These instructions consist mostly of register-to-register operations . Only load and store instructions access memory . Since almost all instructions make use of

register addressing, there are only a few addressing modes in a reduced instruction set computer and there are a large number of general-purpose registers .

RISC instructions complete execution in one machine cycle using pipelining technique.

->Pipelining is the technique allows the next instruction to enter the execution cycle while the previous instruction is still processing .

i.e when when one instrution is being executed ,its successor is being decoded and a third instrution is being fetched from memory.

->ARM7TDMI is a 3 stage pipeline 32 bit RISC processor.

->The processor is characterized by single data and adress bus for instructions and data.

Processor operation states:

The CPU have two instruction sets

1.ARM instruction set -> 32 bit wide instructions n provided max performance

2.Thumb instruction set -> 16 bit wide n provide max code density.instructin operate on 8,15,32 bit data types.

The THUMB Concept:

ARM7TDMI employes a unique architectural stragey known as THUMB which is suited for application where memory is issue or code density is issue.

THUMB followed super reduced instruction set.it sets 16 bit instrution lenght allows it to approach twice the density of standard arm code at the same time

retaining most of the ARM's advantage over a traditional 16 bit processor .

Thumb operated on the same 32 bit register set as ARM code.

Each 16 bit Thumb instruction has a corresponding 32 bit ARMinstruction with the same effect on the processor model.

ADV of ARM instruction

To manupulate 32 bit integers with single instructions and to address a large address space effectively.

ADV of Thumb

Abitlity to swictch back to full ARM code and execute at full speed.critical loops like

-fast interrups

-DSP algorithms can be coded using the full ARM instrution and linked with THUMB.

Switching state:

-> 1.Entering into THUMB state can be achieved by executing a BX intruction with the state bit (bit 0) set in the operand register.

2.Transition to thumb state will also occur automatically on return from an exception like IRQ,FIQ,UNDEF,ABORT,SWI if the exception was entered with the processor in THUMB state.

->Entering ARM stage can be achieved on execution of the BX instruction with the state bit clear in the operand register.

2.On the processor taking an exception like ( IRQ,UNDEF,FIQ,ABORT,SWI,RESET)

Memory format:

ARM7TDMI views memory as linear collection of bytes numbered upward from 0. bytes 0 - 3 hold the first stored word.

ARM7TDMI treat words in memory in two ways

1.BIG Endian-> MSB is at lowest address, word is addressed by the byte address of MSB

2.Little Endian.->LSB is at lowest address,word is addressed by the byte address of LSB.

Operating modes:

ARMTDMI supports seven modes of operation

1.USER ( usr )-> The normal ARM program execution

2.FIQ ( fiq) -> Designed to support a data transfer of channel process.

3.IRQ( irq) ->Used for general purpose interrupt handling.

4.Supervisor( svc)-> Protected mode for the operating system.

5.Abort mode(abt) ->Entered after a data or instruction prefetch abort.

6.System (sys) ->A previlaged user mode for the operating system

7.Undefined (und) ->Entered when an undefined instrution is executed.

Mode changes is under software control , or by external interrupt or exceptions.

In order to service interrupts or exception or to access protected resource the cpu entered non user moders know as previleged modes.

Registers->Total 37 registers - 31 GPIO 32 bit and 6 status registers.

---------------

->The ARM7TDMI is memeber of the advanced RISC MAchines ( ARM) family of general purpose 32 bit microprocessor.

->offers hifh performance for very low power consumption and price.

->It architecture is based on reduced instruciton set computer( RISC)

what is difference between RISC and CISC?

RISC->Reduced instrution set computer

CISC->Complex instrution set computer

Complex instructions came about in order to maximize the performance of early computers. At that time, computers executed instructions sequentially. The first instruction had to complete the execution cycle before the next instruction could begin. Designers combined sequences of instructions into single instructions. This reduced the amount of time spent retrieving instructions from memory , although these instructions did require multiple clocks cycles to execute.

RISC architecture makes use of a small set of simplified instructions in attempt to improve performance . These instructions consist mostly of register-to-register operations . Only load and store instructions access memory . Since almost all instructions make use of

register addressing, there are only a few addressing modes in a reduced instruction set computer and there are a large number of general-purpose registers .

RISC instructions complete execution in one machine cycle using pipelining technique.

->Pipelining is the technique allows the next instruction to enter the execution cycle while the previous instruction is still processing .

i.e when when one instrution is being executed ,its successor is being decoded and a third instrution is being fetched from memory.

->ARM7TDMI is a 3 stage pipeline 32 bit RISC processor.

->The processor is characterized by single data and adress bus for instructions and data.

Processor operation states:

The CPU have two instruction sets

1.ARM instruction set -> 32 bit wide instructions n provided max performance

2.Thumb instruction set -> 16 bit wide n provide max code density.instructin operate on 8,15,32 bit data types.

The THUMB Concept:

ARM7TDMI employes a unique architectural stragey known as THUMB which is suited for application where memory is issue or code density is issue.

THUMB followed super reduced instruction set.it sets 16 bit instrution lenght allows it to approach twice the density of standard arm code at the same time

retaining most of the ARM's advantage over a traditional 16 bit processor .

Thumb operated on the same 32 bit register set as ARM code.